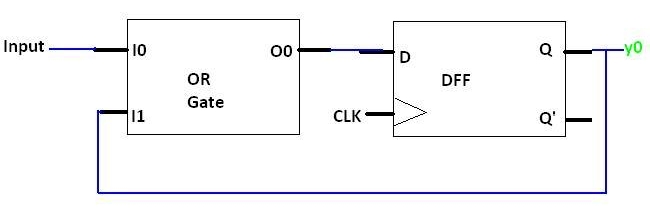

I'm not sure whether the following scheme is valid:

As now, instead of having the input to be steady for Tsetup before the clock's rising, it needs to be steady for Tsetup + T(OR_GATE).

(Where T(OR_GATE) is the time it takes to the OR gate to output a valid value).

What do you think please?

Thank you.

As now, instead of having the input to be steady for Tsetup before the clock's rising, it needs to be steady for Tsetup + T(OR_GATE).

(Where T(OR_GATE) is the time it takes to the OR gate to output a valid value).

What do you think please?

Thank you.