Hi guys!

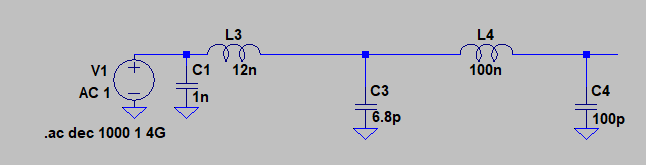

I have recently changed my schematic to reflect the non-ideal nature of the passive filters in the circuit (aka inductor and capacitor).

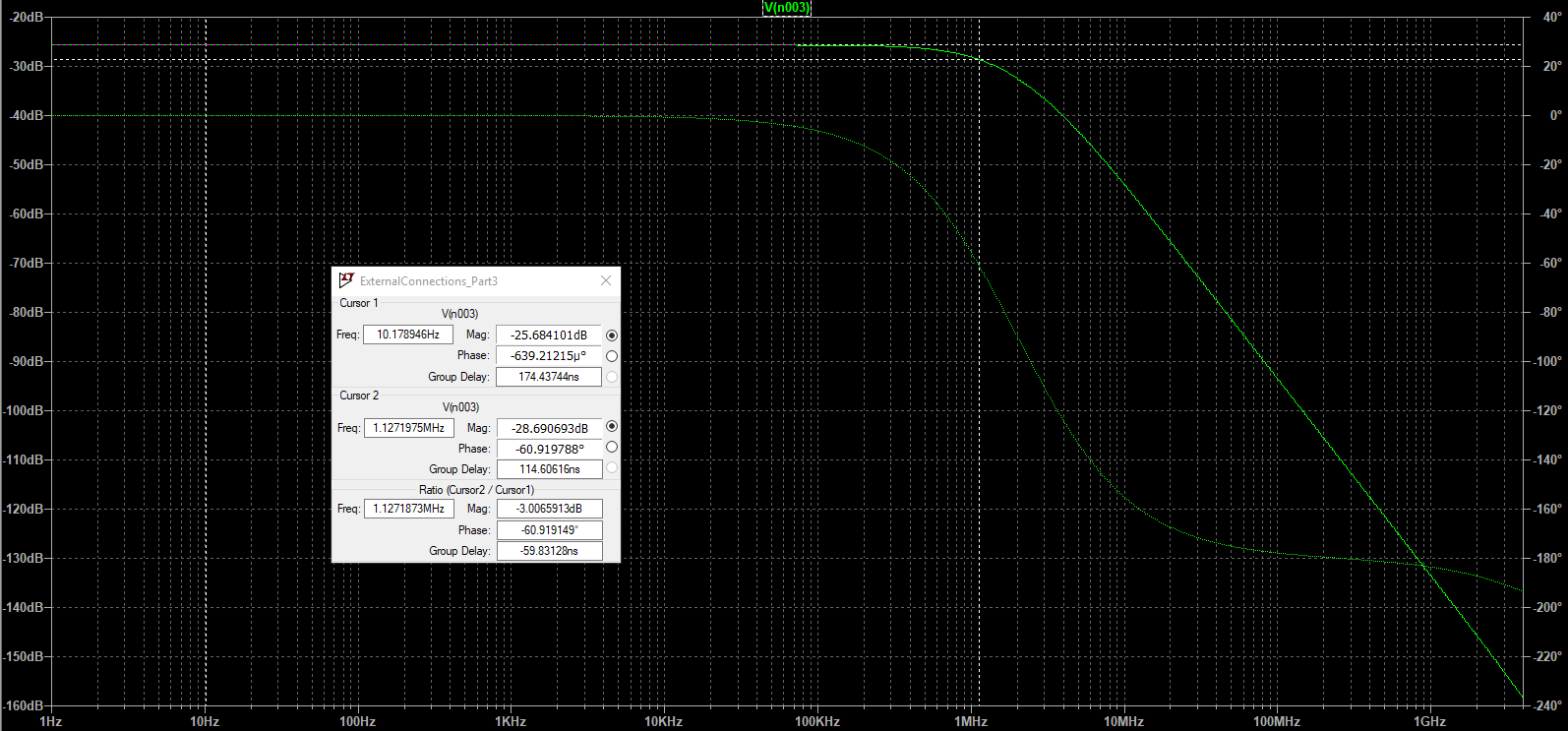

the output graph, taken at the node at the end seems to mimic a low pass filter but my desired output is with regards to an output of 30MHz and the concern i have is with regards to the harmonics of my carrier frequencies, thought of to be 24MHz, 102 and 360 MHz affecting and distoring my signal.

Sadly i have no idea how to interpret the graph.

Can anybody aid me and share their insight on my circuit?

am i also right to say that the cut-off freq, at 3db, is 1.2719MHz.

Thank you in advance.

This forum has been amazing!

I have recently changed my schematic to reflect the non-ideal nature of the passive filters in the circuit (aka inductor and capacitor).

the output graph, taken at the node at the end seems to mimic a low pass filter but my desired output is with regards to an output of 30MHz and the concern i have is with regards to the harmonics of my carrier frequencies, thought of to be 24MHz, 102 and 360 MHz affecting and distoring my signal.

Sadly i have no idea how to interpret the graph.

Can anybody aid me and share their insight on my circuit?

am i also right to say that the cut-off freq, at 3db, is 1.2719MHz.

Thank you in advance.

This forum has been amazing!