Thank you, Mr Al and Jony.

@Mr Al.

First, a PMOS is driven from the ground up, such that the closer the gate is to ground the more it conducts.

Yes, I know that. The current through PMOS increased significantly as the voltage Vsg increases a little.

That means as long as there is input voltage there is always enough gate voltage available.

Vin = Vs

Vsg = Vin - Vg

Vsg will be always positive provided that Vin is larger than Vg.

Did you mean that the voltage Vg is always smaller than Vin?

Vg is the output voltage of error amplifier.

I assume that in this case the DC voltage sources for the error amplifier is also VDD. In that case as Jony said, Vout = Vg, at best, is VDD. Generally Vg will be smaller than VDD.

And it makes sense as you said, provided there is Vin, Vsg will be always larger than zero and the transistor never turns off.

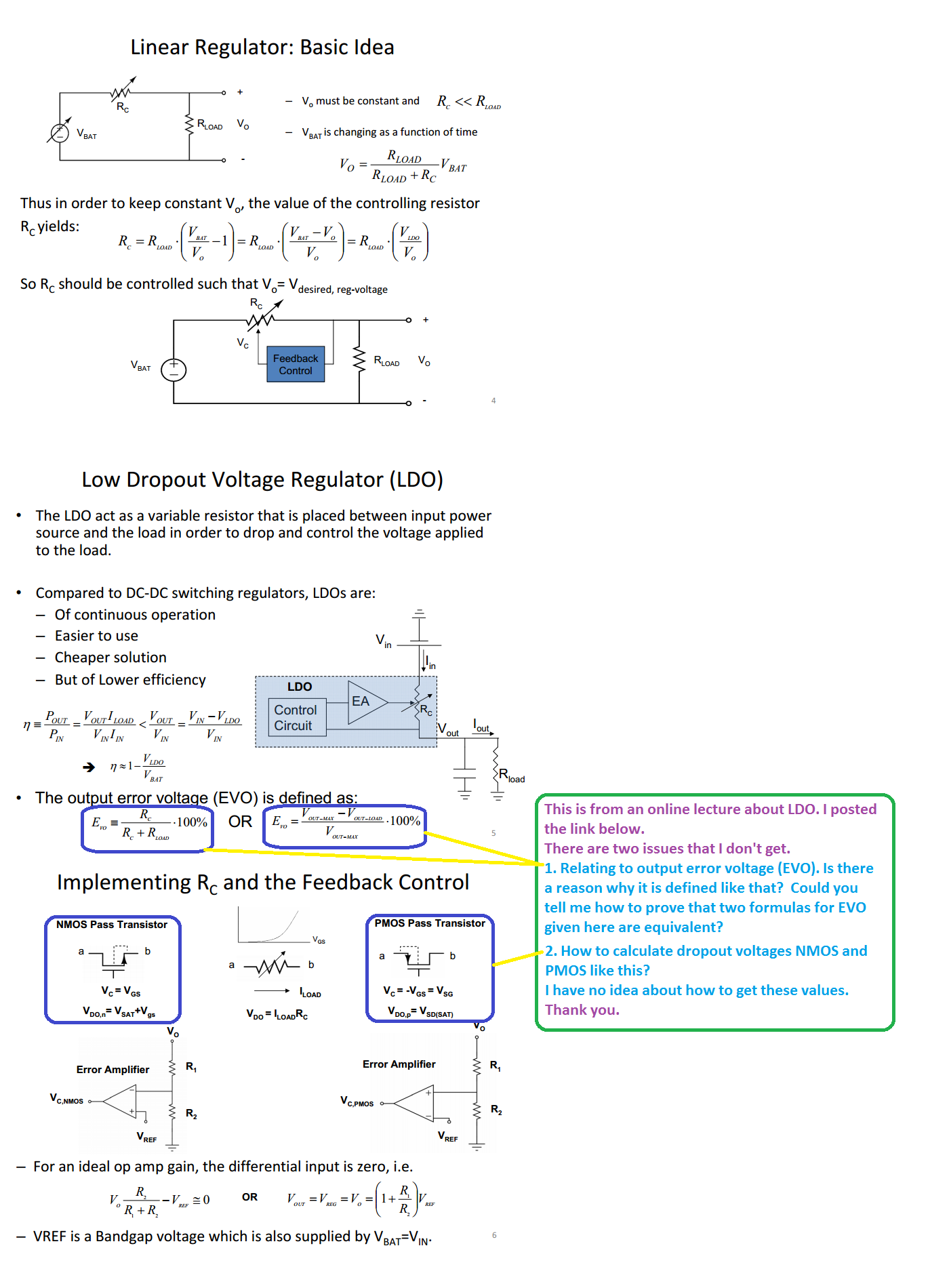

But for NMOS there is not always enough gate drive available because the gate has to be higher than the source, and if the source is already very close to the drain (the drain gets the input voltage level applied to it, which is the maximum available voltage in the system) this means the gate voltage will always be lower than the level needed to drive the NMOS source very very close to the input voltage level (that's LDO operation).

Could you give an example in which the gate voltage is not enough?

Here is what I can imagine.

Input voltage: Vin = Vd: 2.3 - 2.9V

Output volage: Vout = Vs = 2V

Assuming that the error amplifier also uses Vin as DC voltage sources for biasing.

At the time Vin = 2.3V and Vout = 2V => Vdrop = Vds = 0.3V.

The maximum output voltage of error amplifier (best case) is Vin - 1 = 1.3V.

And therefore, Vgs < 0 and the transistor is off.

However, is there a perfect error amplifier that will give output voltage equal to DC voltage?

For example, if VDC = 2V then the output voltage of error amplifier will be 2V.

Jony:

I see your problem now, you simply forgot how NMOS voltage follower work.

As a reminder can you tell me what is the output voltage (Vout) in these three simple circuits? You can assume Vgs = 3V

My problem is that I usually can't accept that Vgs is almost constant as in the case of emitter follower.

If we consider Vgs is constant.

a) Vout = 5 -3 = 2V

b) Vout = 10 -3 = 7V

c) Vout = 23 -3 = 20V

Are you sure about that ?

I thought it is PMOS in your picture.

If it is NMOS then it is common drain.

In that picture, how can you know that Vds(min) = 3.5V?

Do you understand this now ?

I am still confused about the statement saying that Vdrop in NMOS is higher than that in PMOS. It seems to me that we use PMOS instead of NMOS for the reason mentioned by Mr Al not because Vdrop of NMOS is higher than PMOS.

P.S. In case of PMOS, why don't we use an error amplifier which is Vout very large?

For example, with the circuit Vin: 2.3 -3V, we use an error amplifier that give maximum output voltage about 4V.