Hi,

Sorry for asking this question again. I really got stuck.

Here are two pages from this lecture slide about power amplifier: https://course.ee.ust.hk/elec518/lect11.pdf

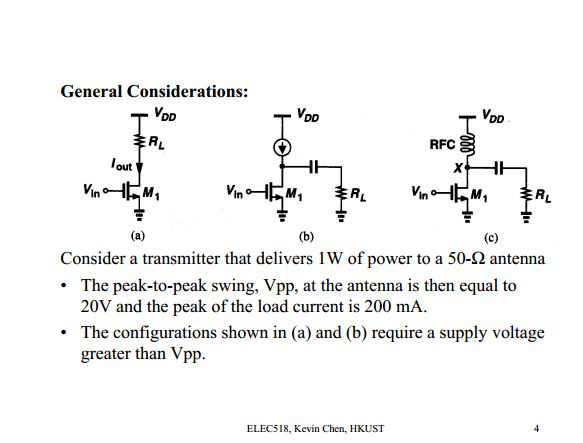

Q1: I know that Vx can swing from 0 to 2VDD but why this can be used to lower supply voltage by a factor of two?

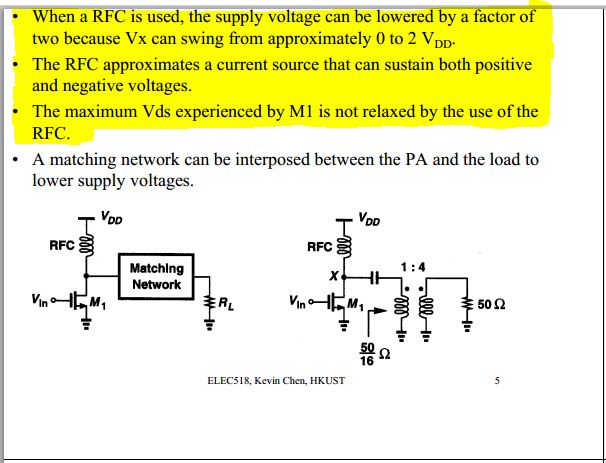

Q2: The RFC approximates a current source. Yes, but what does they mean in "The RFC approximates a current source that can sustain both positive and negative voltages."

Q3 lease help me understand this "The maximum Vds experienced by M1 is not relaxed by the use of the RFC."

lease help me understand this "The maximum Vds experienced by M1 is not relaxed by the use of the RFC."

Thank you.

Sorry for asking this question again. I really got stuck.

Here are two pages from this lecture slide about power amplifier: https://course.ee.ust.hk/elec518/lect11.pdf

Q1: I know that Vx can swing from 0 to 2VDD but why this can be used to lower supply voltage by a factor of two?

Q2: The RFC approximates a current source. Yes, but what does they mean in "The RFC approximates a current source that can sustain both positive and negative voltages."

Q3

Thank you.