Hi,

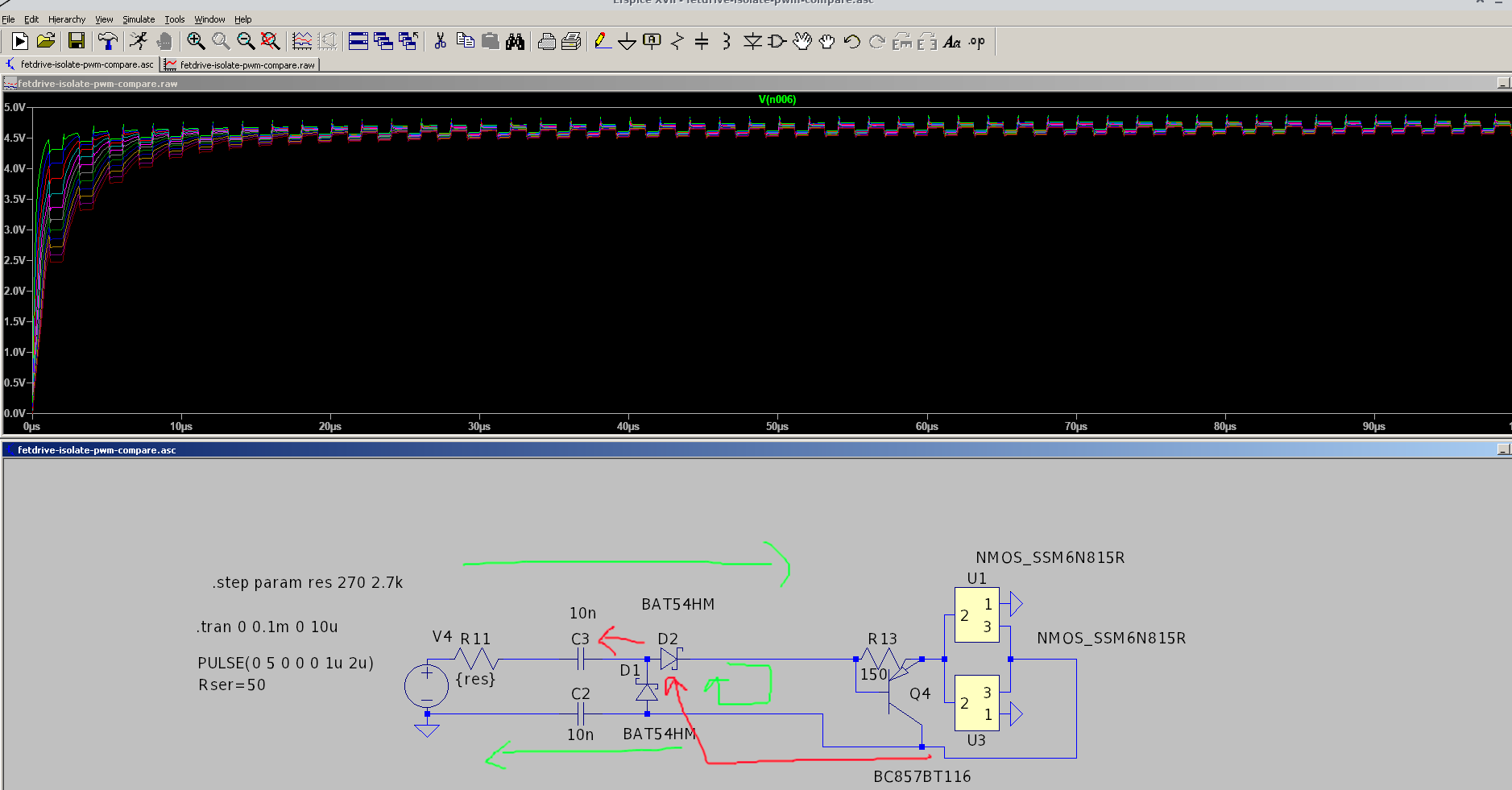

Just hoping for another set of eyes to ensure I've got this right. Here's an isolated fet driver circuit with fast discharge.

I thought R11 with C3 would act as a filter but the value isn't having much an effect. My understanding is C3 allows the PWM to pass, too small a value and the PWM frequency won't get through (so C3 is the main part of the filter).

The driver switches low frequency, low voltage AC but the AC is rectified someplace else and ends up providing the PWM, therefore there's a loop and potentially high frequency noise and the alike could follow the red arrow back to the voltage source (and blow it), therefore the voltage source requires a TVS and a higher value of C3 works to restrict said noise from making it back in the first place.

PWM frequency is at least 1MHz to keep the FET on using it's internal gate capacitance.

While I'm at it, the fast gate discharge I nicked from another circuit and while it simulates as working I'm curious as to how. Being a PNP I expected the gate had to be pulled down to ground to discharge whereas when the PWM stops both the voltage at gate/emitter is at the same value, other than a *very* minor voltage drop by way of the diode reverse current and R13?

Just hoping for another set of eyes to ensure I've got this right. Here's an isolated fet driver circuit with fast discharge.

I thought R11 with C3 would act as a filter but the value isn't having much an effect. My understanding is C3 allows the PWM to pass, too small a value and the PWM frequency won't get through (so C3 is the main part of the filter).

The driver switches low frequency, low voltage AC but the AC is rectified someplace else and ends up providing the PWM, therefore there's a loop and potentially high frequency noise and the alike could follow the red arrow back to the voltage source (and blow it), therefore the voltage source requires a TVS and a higher value of C3 works to restrict said noise from making it back in the first place.

PWM frequency is at least 1MHz to keep the FET on using it's internal gate capacitance.

While I'm at it, the fast gate discharge I nicked from another circuit and while it simulates as working I'm curious as to how. Being a PNP I expected the gate had to be pulled down to ground to discharge whereas when the PWM stops both the voltage at gate/emitter is at the same value, other than a *very* minor voltage drop by way of the diode reverse current and R13?